摩尔规律终究还能走多远?一旦摩尔规律正式走入前史,半导体工业该怎么持续向前跨进?而在所谓的「后摩尔规律年代」,IC业者面对的应战是什么?又该怎么因应?

现在已近九旬高龄的英特尔(Intel)一起创办人Gordon Moore在1965年宣告了一篇文章,提出了IC上电晶体数量会在接下来十年依循每年添加一倍的规矩开展,这今后这个理论依据数次演化,成为全球半导体工业界奉为圭臬的「摩尔规律」(Moores Law),随同IC商场阅历半世纪的蓬勃开展,催生很多让群众日常日子愈加便当、更五光十色的科技。

2015年,摩尔规律欢庆50周年,Moore本人在承受IEEE期刊《Spectrum》专访时表明,其实他在宣告那篇文章的时分仅仅共享一个趋势调查,由于其时IC技能正在改动整个电子工业的经济形式、却未被遍及供认;而他彻底没有想到那样的一个理论竟然被记住那么久,乃至被称为驱动工业开展的「规律」。

不过摩尔规律终究不是以谨慎科学程序所界说的真实「规律」,Moore自己也说,那仅仅一种调查与估测;许多人猜测摩尔规律将在2015至2020年失效,而在2012年左右,摩尔规律开端出现速度趋缓的显着痕迹,当年全球半导体工业营收暨2011年仅2.1%的生长之后不升反降,出现了2.6%的负生长,接下来几年的营收体现也一片低迷,不光不复以往动辄两位数字的生长体现,在2015年还再度出现了2.3%的负生长。

半导体厂商们发现,要保持摩尔规律持续推进的本钱变得越来越巨大,制程微缩不再跟跟着电晶体单位本钱跟着下降的效应,工业界从32/28纳米节点跨进22/20纳米制程节点时,首度遭受了本钱上升的状况;业界专家们将原因指向了迟迟未能「上台面」的极紫外光(EUV)微影技能,就由于该新一代微影技能仍未能顺畅诞生,使得22纳米以下的IC仍得透过多重图形(multi-patterning)办法来完结,这意味着杂乱的规划流程、高危险,以及昂扬的本钱。

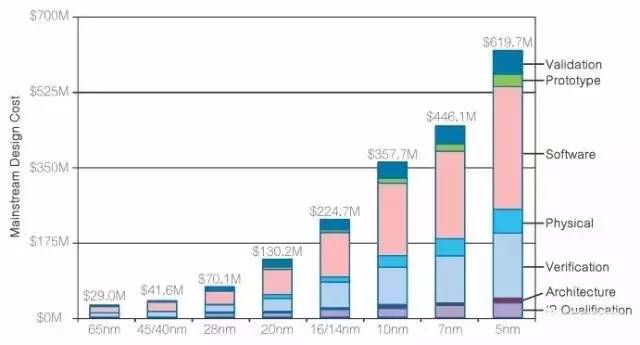

商场研究组织International Business Strategies (IBS)的资深半导体工业分析师Handel Jones估量,当半导体制程走向5纳米节点,IC规划本钱将会是现在现已非常昂扬之14/16纳米制程规划本钱的三倍(图1),因而规划业者「需求有非常很多的销售额才干收回出资。」

摩尔规律终究还能走多远?一旦摩尔规律正式走入前史,半导体工业该怎么持续向前跨进?而在所谓的「后摩尔规律年代」,IC业者面对的应战是什么?又该怎么因应?

在一场1月初于美国加州举办、由世界半导体工业协会(SEMI)主办的年度工业战略顶峰会(Industry Strategy Symposium,ISS)上,来自半导体工业界的专家指出,假如EUV技能在2020年顺畅面世,半导体技能演进还能持续到2025年。

工业参谋组织IC Knowledge总裁Scotten Jones在该场顶峰会上表明:「我不以为摩尔规律已死,从事深度技能研制的人也不以为;」他指出,大厂英特尔(Intel)与Globalfoundries都泄漏半导体制程在后14纳米(post-14nm)节点能到达本钱节约,「我信任咱们有办法制作出让本钱下降的新一代电晶体。」

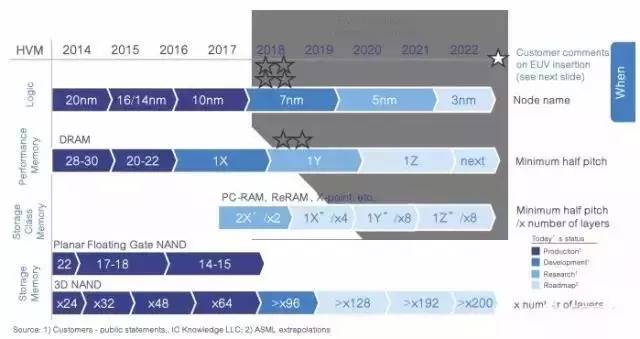

Jones猜测5纳米节点将在2019年开端在某些制程过程选用EUV技能,或许仍得选用某种方式的FinFET电晶体;至于再往下到3.5纳米节点,将会开展至选用水平纳米线(horizontal nanowire),而该节点应该会是经典半导体制程微缩的结尾;这今后2.5纳米节点堆叠n型与p型纳米线%。

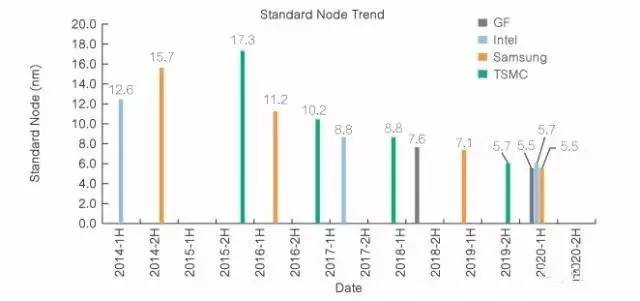

关于EUV终究何时能正式「上阵」,商场研究组织Semiconductor Advisors的分析师Robert Maire以为:「EUV微影线年;」他指出,台积电(TSMC)现已宣告了将在5纳米节点选用EUV微影的计画;而英特尔则或许会在7纳米选用EUV微影,与台积电的5纳米节点量产时程适当,时程估量是在2019年。

而Globalfoundries技能长Gary Patton在2016年10月来台与本地媒体共享该公司最新技能与战略方向时则表明,他预期EUV微影技能要到2019年才会迈入老练,而Globalfoundries在该时刻点之前就会量产的7纳米制程应该不会选用该技能。

现在在商场上只要来自荷兰的设备业者ASML能供给EUV微影体系,是该公司投入了三十年时刻与巨大研制本钱的效果,而该公司乃至获得了英特尔、台积电与三星(Samsung)等半导体大厂的联合出资,这些股东们的首要方针便是加快EUV技能的完结。ASML发言人表明:「咱们预期EUV微影将在个位数纳米制程节点被使用于记忆体中的两个或更多层;而在最先进的逻辑制程节点(7或5纳米),则被使用于6~9层。」

ASML的第一代(选用0.33NA光学镜片、完结约13纳米的线宽) EUV微影设备NXE:3400B将在本年正式出货,预期吞吐量可达每小时125片晶圆、微影叠对(overlays)差错容许度在3纳米以内;该公司表明已有4家逻辑芯片制作商、2家记忆体芯片制作商表明将在2018年左右选用第一代EUV体系进行量产。

选用今天的滋润式微影设备需求以多重光罩才干完结的电路图形,若选用0.33NA的EUV体系预期只需求单一光罩过程就可完结;不过半导体制程若再持续往更纤细节点跨进,就算选用EUV设备也或许需求多重图形过程。

为此ASML于上一年11月就宣告以11亿美元收买光学大厂蔡司(Carl Zeiss)的24.9%股份,两边将联手研制数值孔径(numerical aperture,NA)高于0.5的版别,不过此第二代EUV微影要到2024年今后才会量产,将能完结约8纳米的线片晶圆产值、叠对差错容许度小于2纳米。

ASML技能长Martin van den Brink在宣告上述协作案时的新闻声明中指出,新一代(0.5NA)体系将「可在次3纳米节点为芯片制作商防止杂乱且贵重的0.3NA体系多重图形过程,以单次曝光援助高生产力,并可下降单位本钱。」

不过商场研究组织VLSI Research总裁Risto Puhakka表明,工业界人士仍广泛预期,在第二代EUV体系于2024年左右面世从前,恐怕仍是得运用第一代0.33NA微影体系进行多重图形。「仅仅需求几重图形、以及会需求多久时刻?」他也指出,以往ASML不曾直接出资供给链上的任何厂商,并且是以大手笔收买高份额股份,显见要打造更新一代EUV体系是高危险使命,并且ASML势在必得。

看来假如一切顺畅,2018年就能看到第一批选用EUV微影设备量产的先进制程节点IC;但机台尺度简直同等一间小房间的EUV,一台要价逾越1亿美元(至少31亿台币),这意味着除非是财力够雄厚的半导体厂商,很难担负此顶级技能的出资。

而千呼万唤始出来的EUV微影设备就算线年之后顺畅上线量产,在终端使用商场如PC、才智型手机等生长阻滞、缺少很多需求的趋势下,选用该设备之先进制程初期本钱与危险必然依然偏高,IC业者假如想只靠EUV来保持摩尔规律「制程越微缩、电晶体单位本钱越低」的理论,恐怕并不简单。

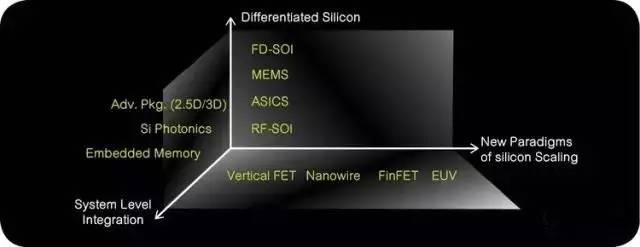

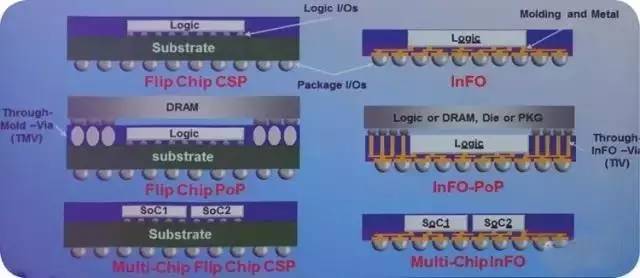

也到会了本年1月美国ISS 的Globalfoundries技能长Patton在专题讲演中表明:「摩尔规律将完结仅仅一个观点,咱们总是能找出怎么推进工作演进的办法;」他以为,芯片业者现在有必要要在制程以及封装技能方面寻求不同方向的立异(图4),「整个工业环境跟我入行的时分现已彻底不一样了。」

图4:除了跟随摩尔规律,Globalfoundries技能长Gary Patton以为IC业者应该寻求不同方向的制程与封装技能立异

在半导体工业界具有逾越三十年阅历的Patton,在从前向台湾本地媒体简报Globalfoundries技能战略时表明,今天商场上有各式各样新兴起的电子设备与终端使用,例如举动运算、普适运算( pervasive computing,例如无所不在的连网才智设备)以及人工才智(AI)、虚拟/扩增实境(AR/VR)…等等,单一技能并不一定合适一切使用的需求。

Patton表明,人工才智、云端运算、高速通讯等使用,现在最顶级的3D电晶体FinFET制程是抱负挑选,现在该技能进入14纳米节点量产、现已老练并且对高阶使用有价值;至于对运算功能要求较低、也以较低功率运作的各种嵌入式设备,例如物联网设备,其实就不一定要用到最顶级的FinFET制程,不然并不契合本钱效益。

GlobalFoundries供给的其他技能选项是全空乏绝缘上覆矽(Fully depleted silicon-on-insulator,FD-SOI)制程;Patton指出,该公司预备在2017年量产的22纳米FD-SOI制程,在本钱上与老练的28纳米平面电晶体制程适当,但能到达相似FinFET制程的功能,并且功耗更低、封装尺度更小,也更合适与RF元件的整合。

在封装技能方面,Patton表明在曩昔一年来,Globalfoundries看到2.5D与3D芯片堆叠的客户需求有大幅生长的趋势;现在该公司可供给给用于32~22纳米深度沟槽式晶圆的「才智中介层」(interposer),具有去耦电容,能援助低功率使用的芯片堆叠。

在芯片堆叠技能方面,台湾半导体工业协会(TSIA)理事长、钰创科技董事长卢出众表明,曩昔15年来IC工业现已达成了「相似以微观修建技能造楼房」的打破,创造3D乃至逾越3D的异质性晶粒摆放或堆叠办法;再加上半导体厂商在晶圆级封装技能(WLP)上的研制效果──例如台积电的整合型扇出(Integrated Fan-out,Info)与整合型扇出-封装内建封装技能(InFO-PoP)──将IC制作与封测一体化,会是让摩尔规律连续更长寿数的要害。

卢出众以为,InFO以及由于InFO而得以完结的另一种直通互连通孔(TIV)立异技能,将推进IC工业进入在制程微缩一起叠加IC、让纳米技能经济效益扩大的「矽代代4.0」 (Silicon 4.0);未来矽芯片能够直接连接如光学透镜、感测器或致动器等现在嵌入于体系中但仍未微型化的元件,而这也是晶圆代工厂、IC规划业者和体系厂商打开协作的新时机。

其实,不管摩尔规律会不会、何时走向完结,IC工业在此时应该现已意识到,这个世界现已变了…新出炉的Gartner初步统计成果闪现,从2012年开端走下坡的全球PC商场出货量在2016年又一次出现6.2%的阑珊;至于现已替代PC成为推进半导体工业主力的才智型手机商场,看来在接下来几年也将仅存个位数的温文生长。

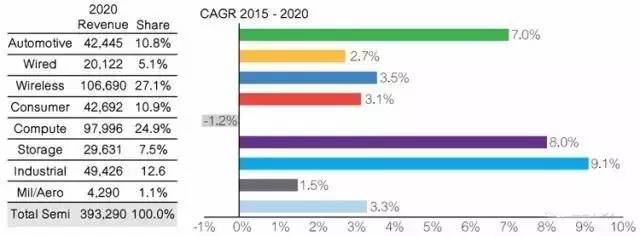

新兴起的物联网商场尽管逐步从一片混沌中闪现规模经济以及有规矩可循的商业形式,多样少数的芯片需求对传统IC业者来说还得阅历好一段习惯期;汽车商场由于开端选用连网技能、各种感测器以及人工才智计划,俨然成为IC商场的最新「杀手级使用」,但汽车工业的保存性情好像还未彻底跟着这些新技能的选用而改动,要打入车用供给链对没有相关阅历的半导体厂商来说又是一个应战。

EDA大厂明导世界(Mentor Graphics)执行长Walden C. Rhine (Wally)在上一年8月于台湾举办的年度技能论坛上表明,半导体工业营收生长近几年出现阻滞,有很大一部份原因是包括Apple、Samsung等选用自家规划之芯片的体系厂商,并未将IC营收揭露,但光是Apple与三星两家公司在客制化手机处理器的兼并市占率或许就逾越30% ,那些被「躲藏」的估量高达100亿美元。

当Apple、Google…等等原本是IC业者「大客户」、乃至仅仅「直接客户」的终端体系/网路业者都开端由于各自的一起需求而亲自投入IC规划,就算半导体制程微缩技能应战都能顺畅战胜、摩尔规律能千秋万岁,IC厂商也很难再依循旧有的事务形式获取赢利,有必要开辟新的商场/客户、寻求新的协作时机。

EDA供给商新思(Synopsys)董事长暨一起执行长Aart de Geus在上一年9月于台湾举办的新思年度运用者大会承受拜访时表明,身为IC规划东西供给商,他们现已发现到近两年与体系厂商互动与协作的时机添加许多,也让他们的生意形式有必要有所改动;而他也以为,在新的工业生态下要取得成功,协作变得非常重要,包括与跨范畴厂商以及同业之间的协作。

而除了寻求同业/异业协作,包括Mentor的Wally以及另一家EDA供给商益华电脑(Cadence)总裁暨执行长陈立武、资深副总裁暨战略长徐季平,都不只一次提到了体系规划才能的重要性;这关于以往只特长硬体技能、缺少软硬体整合才能与体系观的IC规划业者来说会是特别需求警觉检讨的议题。

对半导体IC业者来说,其实在所谓的「后摩尔规律年代」,最大的应战并非打破技能的极限,而是能不能敏锐地意识到工业生态的改变、打破旧有的考虑结构与事务形式,规划出最有利于未来开展的新战略/新路线。

在半导体制作/封测与设备范畴,各家大厂现已开端透过一起出资、协作的形式,将研制资源做最大化会集,催生能推进各种新使用的新一代技能;而在IC规划范畴,技能上的应战能凭借各家EDA供给商的最新一代东西,本钱问题也能够透过制作业者供给的多元化技能选项找到最恰当的折衷计划,更重要的是在改变剧烈的商场摸清方向。

台湾声称具有包括半导体上、中下游的最完好IC工业链,还有一家在全球晶圆代工商场占有率高达六成的「国宝」台积电;但是从前生气蓬勃的IC规划业在近几年来体现未有打破,厂商之间的技能同质性也偏高,现有业者假如不能把握转型关键,在全球半导体工业生长阻滞的趋势下,出路堪虑。

整并当然也是一个选项,但寻求新的事务形式与协作时机,是台湾IC规划业者的燃眉之急;Synopsys的de Geus就主张,台湾IC规划应该先厘清有那些技能/使用范畴是要持续开展,以及有哪些范畴是能够寻求对外协作的。他表明,以物联网使用为例,这是一个正在起步的新商场,台湾业者假如能把握先机树立有用的事务形式,就有成功的时机。

而Mentor的Wally则主张台湾IC规划业者寻求产品的差异化,可投入在物联网使用非常抢手的类比/混合信号、RF或MEMS等技能范畴;他以为台湾以中小企业为主的IC规划厂商仍具有较具灵活性的优势,比起大型业者更能探究、测验新使用范畴。